Decodificador de endereços

Este artigo não cita fontes confiáveis. (Agosto de 2021) |

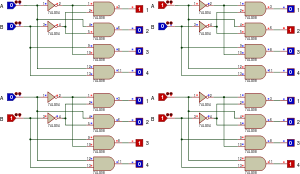

Em eletrônica digital, um decodificador de endereços (ou descodificador, em Portugal) é um circuito que possui dois ou mais bits de um barramento de endereços como entradas e que possui um ou mais dispositivos de seleção de linhas como saída. Quando os endereços para um dispositivo em particular aparecem no barramento de endereços, o decodificador de endereços confirma a linha de seleção para aquele dispositivo. Um decodificador de endereços separado de dispositivo único pode ser incorporado em cada dispositivo em um barramento de endereços, ou um decodificador de endereço único pode servir múltiplos dispositivos. No último caso, um decodificador de endereços com N bits de endereços de entrada pode servir a até 2N dispositivos separados. Vários membros da série 7400 de CIs são decodificadores de endereços. Um exemplo é o TTL 74154. Este decodificador de endereços possui quatro endereços de entrada e 16 (isto é, 24 ) linhas de seleção de saída. Um decodificador de endereços também é denominada de "demultiplexador" ou "demux," embora estes termos sejam mais genéricos e possam referir-se a outros dispositivos além de decodificadores de endereços. O TTL 74154 acima mencionado pode ser chamado de "demux 4-para-16".

Decodificadores de endereços são blocos de construção fundamentais para sistemas que usem barramentos. Eles estão representados em todas as famílias de circuitos integrados e em todas as bibliotecas-padrão FPGA e ASIC. São discutidos em textos introdutórios em design de lógica digital.