Latch-up

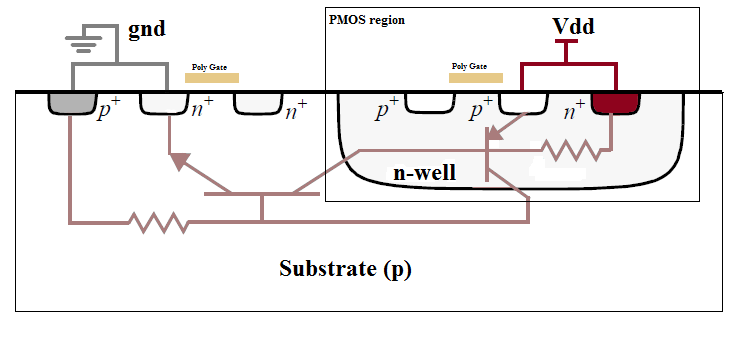

O Latch-up é um efeito de descarga elétrica que pode ocorrer em circuitos integrados (CI). O efeito de latch-up é análogo a um curto circuito, quando um caminho de baixa impedância é formado entre os trilhos (rail) de alimentação de um circuito CMOS. Tal efeito é capaz de ocasionar erros na operação lógica do circuito até como a destruição do mesmo devido ao excesso de corrente.

A estrutura parasítica capaz de ocasionar o Latch-up, é similar a um tiristor (SCR), uma estrutura do tipo PNPN.

O caminho de baixa impedância pode se dar pelos mais diversos motivos e.g., pela distância entre difusões do tipo P e do tipo N, pela falta de polarização dos poços, etc.

Boas Práticas

O Latch-up pode ser causado pela má polarização do substrato, assim diversas técnicas[1][2] podem ser tomadas em nível de leiaute e projeto para se evitar o efeito. Em circuitos digitais que não fazem uso das células de well tap, utiliza-se do incremento do número de contatos para polarização do substrato. Em circuitos modernos que fazem uso de well taps, se faz a redução da distancia de posicionamento das mesmas melhorando assim a polarização do substrato pelo circuito.

- ↑ C. Whitaker, Jerry (2018). Microelectronics. [S.l.]: CRC Press. p. 7-7

- ↑ «Understanding Latch-Up in Advanced CMOS Logic» (PDF). 1998