Barramento (computação)

Na arquitetura de computadores, um barramento[1] (forma abreviada do latim omnibus, e históricamente também chamado de data highway (entrada de dados)[2] ou databus) é um sistema de comunicação que transfere dados entre componentes dentro de um computador, ou entre computadores. Esta expressão abrange todos os componentes de hardware (fios, fibra óptica, etc.) e software relacionados, incluindo protocolos de comunicação.[3]

Os primeiros barramentos de computador eram fios elétricos paralelos com múltiplas conexões de hardware, mas o termo agora é usado para qualquer arranjo físico que forneça a mesma função lógica de um barramento elétrico paralelo. Os barramentos de computador modernos podem usar conexões paralelas e seriais de bits e podem ser conectados em uma topologia multidrop (paralelo elétrico) ou em cadeia, ou conectados por hubs comutados, como no caso do Universal Serial Bus (USB).

Background e nomenclatura

editarOs sistemas de computador geralmente consistem em três partes principais:

- A unidade central de processamento (CPU) que processa dados,

- A memória que contém os programas e dados a serem processados, e

- Dispositivos de E/S (entrada/saída) como periféricos que se comunicam com o mundo exterior.

Um computador antigo pode conter uma CPU de tubos de vácuo conectada manualmente, um tambor magnético para a memória principal e uma fita perfurada e uma impressora para leitura e gravação de dados, respectivamente. Um sistema moderno pode ter uma CPU multi-core, DDR4 SDRAM para memória, uma unidade de estado sólido para armazenamento secundário, uma placa gráfica e LCD como sistema de exibição, um mouse e teclado para interação e uma conexão Wi-Fi para rede. Em ambos os exemplos, barramentos de computador de uma forma ou de outra movem dados entre todos esses dispositivos.

Na maioria das arquiteturas de computadores tradicionais, a CPU e a memória principal tendem a ser fortemente acopladas. Convencionalmente, um microprocessador é um único chip que possui várias conexões elétricas em seus pinos que podem ser usadas para selecionar um "endereço" na memória principal e outro conjunto de pinos para ler e gravar os dados armazenados naquele local. Na maioria dos casos, a CPU e a memória compartilham características de sinalização e operam em sincronia. O barramento que conecta a CPU e a memória é uma das características que definem o sistema e geralmente é chamado simplesmente de barramento do sistema.

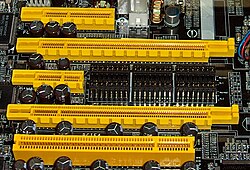

É possível permitir que periféricos se comuniquem com a memória da mesma forma, anexando adaptadores, seja na placa-mãe ou na forma de placas de expansão, diretamente ao barramento do sistema. Isso geralmente é realizado através de algum tipo de conector elétrico padronizado, vários deles formando o barramento de expansão ou barramento local. No entanto, como as diferenças de desempenho entre a CPU e os periféricos variam amplamente, geralmente é necessária alguma solução para garantir que os periféricos não diminuam o desempenho geral do sistema. Muitas CPUs apresentam um segundo conjunto de pinos semelhantes aos de comunicação com a memória, mas capazes de operar em velocidades muito diferentes e usando protocolos diferentes (por exemplo, UART, SPI, e Ethernet). Outros usam controladores inteligentes para colocar os dados diretamente na memória, um conceito conhecido como acesso direto à memória. A maioria dos sistemas modernos combina ambas as soluções, quando apropriado.

À medida que o número de periféricos potenciais crescia, a utilização de uma placa de expansão para cada periférico tornou-se cada vez mais insustentável. Isto levou à introdução de sistemas de barramento projetados especificamente para suportar múltiplos periféricos. Exemplos comuns são as portas SATA em computadores modernos, que permitem a conexão de vários discos rígidos sem a necessidade de uma placa. No entanto, esses sistemas de alto desempenho são geralmente muito caros para serem implementados em dispositivos de baixo custo, como um mouse. Isto levou ao desenvolvimento paralelo de uma série de sistemas de barramento de baixo desempenho para essas soluções, sendo o exemplo mais comum o Universal Serial Bus (USB) padronizado. Todos esses exemplos podem ser chamados de barramentos periféricos, embora esta terminologia não seja universal.

Nos sistemas modernos, a diferença de desempenho entre a CPU e a memória principal cresceu tanto que quantidades crescentes de memória de alta velocidade são incorporadas diretamente na CPU, conhecida como cache. Nesses sistemas, as CPUs se comunicam usando barramentos de alto desempenho que operam em velocidades muito maiores que a memória, e se comunicam com a memória usando protocolos semelhantes aos usados exclusivamente para periféricos no passado. Esses barramentos de sistema também são usados para se comunicar com a maioria (ou todos) os outros periféricos, por meio de adaptadores, que por sua vez se comunicam com outros periféricos e controladores. Tais sistemas são arquitetonicamente mais semelhantes a multicomputadores, comunicando-se através de um barramento em vez de uma rede. Nestes casos, os barramentos de expansão são totalmente separados e não compartilham mais nenhuma arquitetura com sua CPU hospedeira (podendo de fato suportar muitas CPUs diferentes, como é o caso do PCI). O que anteriormente seria um barramento de sistema agora é conhecido como barramento frontal.

Dadas estas mudanças, os termos clássicos “sistema”, “expansão” e “periférico” já não têm as mesmas conotações. Outros sistemas de categorização comuns baseiam-se na função principal do barramento, conectando dispositivos interna ou externamente, PCI vs. SCSI, por exemplo. No entanto, muitos sistemas de barramento modernos comuns podem ser usados para ambos; SATA e o eSATA associado são um exemplo de sistema que anteriormente seria descrito como interno, enquanto certas aplicações automotivas usam principalmente o IEEE 1394 externo de uma forma mais semelhante a um barramento de sistema. Outros exemplos, como InfiniBand e I²C, foram projetados desde o início para serem usados tanto interna quanto externamente.

Barramento interno

editarO barramento interno, também conhecido como barramento de dados interno, barramento de memória, barramento de sistema ou barramento frontal, conecta todos os componentes internos de um computador, como CPU e memória, à placa-mãe. Os barramentos de dados internos também são chamados de barramentos locais, porque se destinam à conexão com dispositivos locais. Esse barramento é normalmente bastante rápido e independente do restante das operações do computador.

Barramento externo

editarO barramento externo, ou barramento de expansão, é composto pelos caminhos eletrônicos que conectam os diversos dispositivos externos, como impressora etc., ao computador.

Barramento de endereço

editarUm barramento de endereço é um barramento usado para especificar um endereço físico. Quando um processador ou dispositivo habilitado para DMA precisa ler ou escrever em um local de memória, ele especifica esse local de memória no barramento de endereço (o valor a ser lido ou escrito é enviado no barramento de dados). A largura do barramento de endereços determina a quantidade de memória que um sistema pode endereçar. Por exemplo, um sistema com um barramento de endereços de 32 bits pode endereçar 2 32 (4.294.967.296) locais de memória. Se cada local de memória contiver um byte, o espaço de memória endereçável será de 4 GiB.

Multiplexação de endereços

editarOs primeiros processadores usavam um fio para cada bit da largura do endereço. Por exemplo, um barramento de endereços de 16 bits tinha 16 fios físicos constituindo o barramento. À medida que os barramentos se tornaram mais largos e mais longos, esta abordagem tornou-se cara em termos do número de pinos do chip e traços da placa. Começando com a DRAM Mostek 4096, a multiplexação de endereços implementada com multiplexadores tornou-se comum. Num esquema de endereço multiplexado, o endereço é enviado em duas partes iguais em ciclos de barramento alternados. Isso reduz pela metade o número de sinais do barramento de endereço necessários para conectar-se à memória. Por exemplo, um barramento de endereços de 32 bits pode ser implementado usando 16 linhas e enviando a primeira metade do endereço de memória, imediatamente seguida pela segunda metade do endereço de memória.

Normalmente, dois pinos adicionais no barramento de controle - um estroboscópio de endereço de linha (RAS) e um estroboscópio de endereço de coluna (CAS) - são usados para informar à DRAM se o barramento de endereço está enviando atualmente a primeira metade do endereço de memória ou A segunda parte.

Implementação

editarAcessar um byte individual freqüentemente requer a leitura ou gravação de toda a largura do barramento (uma palavra) de uma só vez. Nestes casos, os bits menos significativos do barramento de endereços podem nem mesmo ser implementados - em vez disso, é responsabilidade do dispositivo de controle isolar o byte individual necessário da palavra completa transmitida. É o caso, por exemplo, do barramento local VESA que carece dos dois bits menos significativos, limitando este barramento a transferências alinhadas de 32 bits.

Historicamente, também houve alguns exemplos de computadores que só eram capazes de endereçar palavras – máquinas de palavras.

Barramento de memória

editarO barramento de memória é o barramento que conecta a memória principal ao controlador de memória em sistemas de computador. Originalmente, barramentos de uso geral como o VMEbus e o barramento S-100 eram usados, mas para reduzir a latência, os barramentos de memória modernos são projetados para se conectarem diretamente aos chips DRAM, e assim são projetados por órgãos de padronização de chips como o JEDEC. Exemplos são as diversas gerações de SDRAM, e barramentos seriais ponto a ponto como SLDRAM e RDRAM. Uma exceção é o DIMM Fully Buffered que, apesar de ter sido cuidadosamente projetado para minimizar o efeito, tem sido criticado por sua maior latência.

Detalhes de implementeção

editarOs barramentos podem ser barramentos paralelos, que transportam palavras de dados em paralelo em vários fios, ou barramentos seriais, que transportam dados na forma serial de bits. A adição de conexões extras de alimentação e controle, drivers diferenciais e conexões de dados em cada direção geralmente significa que a maioria dos barramentos seriais tem mais condutores do que o mínimo usado em 1-Wire e UNI/O. À medida que as taxas de dados aumentam, os problemas de distorção de tempo, consumo de energia, interferência eletromagnética e diafonia em barramentos paralelos tornam-se cada vez mais difíceis de contornar. Uma solução parcial para este problema tem sido bombear duas vezes o barramento. Freqüentemente, um barramento serial pode operar com taxas de dados gerais mais altas do que um barramento paralelo, apesar de ter menos conexões elétricas, porque um barramento serial inerentemente não tem distorção de tempo ou diafonia. USB, FireWire e Serial ATA são exemplos disso. As conexões multiponto não funcionam bem para barramentos seriais rápidos, portanto, a maioria dos barramentos seriais modernos usa designs de conexão em série ou hub.

Conexões de rede como Ethernet geralmente não são consideradas barramentos, embora a diferença seja mais conceitual do que prática. Um atributo geralmente usado para caracterizar um barramento é que a energia é fornecida pelo barramento para o hardware conectado. Isso enfatiza as origens dos barramentos da arquitetura de barramentos como fornecimento de energia comutada ou distribuída. Isto exclui, como barramentos, esquemas como serial RS-232, Centronics paralelo, interfaces IEEE 1284 e Ethernet, uma vez que estes dispositivos também necessitavam de fontes de alimentação separadas. Os dispositivos Universal Serial Bus podem usar a alimentação fornecida pelo barramento, mas geralmente usam uma fonte de alimentação separada. Esta distinção é exemplificada por um sistema telefônico com modem conectado, onde a conexão RJ11 e o esquema de sinalização modulada associado não são considerados um barramento, e são análogos a uma conexão Ethernet. Um esquema de conexão de linha telefônica não é considerado um barramento no que diz respeito aos sinais, mas o Escritório Central utiliza barramentos com comutadores de barra cruzada para conexões entre telefones.

No entanto, esta distinção—de que a energia é fornecida pelo barramento—não é o caso em muitos sistemas aviônicos, onde conexões de dados como ARINC 429, ARINC 629, MIL-STD-1553B (STANAG 3838) e EFABus (STANAG 3910) são comumente referido como “barramento de dados” ou, às vezes, “barramento de dados”. Tais barramentos de dados aviônicos são geralmente caracterizados por terem vários equipamentos ou itens/unidades substituíveis em linha (LRI/LRUs) conectados a um meio comum e compartilhado. Eles podem, como no ARINC 429, ser simplex, ou seja, ter uma única fonte LRI/LRU ou, como no ARINC 629, MIL-STD-1553B e STANAG 3910, ser duplex, permitindo que todos os LRI/LRUs conectados atuem, em tempos diferentes (half duplex), como transmissores e receptores de dados.[4]

Multiplexação de barramento

editarO barramento do sistema mais simples possui linhas de dados de entrada, linhas de dados de saída e linhas de endereço completamente separadas. Para reduzir custos, a maioria dos microcomputadores possui um barramento de dados bidirecional, reutilizando os mesmos fios para entrada e saída em momentos diferentes.[5]

Alguns processadores usam um fio dedicado para cada bit do barramento de endereço, barramento de dados e barramento de controle. Por exemplo, o STEbus de 64 pinos é composto por 8 fios físicos dedicados ao barramento de dados de 8 bits, 20 fios físicos dedicados ao barramento de endereços de 20 bits, 21 fios físicos dedicados ao barramento de controle e 15 fios físicos dedicados a vários barramentos de energia.

A multiplexação de barramento requer menos fios, o que reduz custos em muitos dos primeiros microprocessadores e chips DRAM. Um esquema comum de multiplexação, a multiplexação de endereços, já foi mencionado. Outro esquema de multiplexação reutiliza os pinos do barramento de endereços como pinos do barramento de dados,[5] uma abordagem usada pelo PCI convencional e pelo 8086. Os vários "barramentos seriais" podem ser vistos como o limite máximo da multiplexação, enviando cada um dos bits de endereço e cada um dos bits de dados, um de cada vez, através de um único pino (ou um único par diferencial).

História

editarCom o tempo, vários grupos de pessoas trabalharam em vários padrões de barramento de computador, incluindo o IEEE Bus Architecture Standards Committee (BASC), o grupo de estudo "Superbus" do IEEE, a iniciativa de microprocessador aberto (OMI), a iniciativa de microsistemas abertos (OMI), o "Gang of Nine" que desenvolveu o EISA, etc.[carece de fontes]

Primeira geração

editarOs primeiros barramentos de computador eram feixes de fios que conectavam a memória e os periféricos do computador. Curiosamente chamados de "tronco de dígitos" no antigo computador CSIRAC australiano,[6] eles receberam o nome de barramentos de energia elétrica, ou barramentos. Quase sempre havia um barramento para memória e um ou mais barramentos separados para periféricos. Estes foram acessados por instruções separadas, com tempos e protocolos completamente diferentes.

Uma das primeiras complicações foi o uso de interrupções. Os primeiros programas de computador executavam E/S aguardando em loop até que o periférico ficasse pronto. Isso foi uma perda de tempo para programas que tinham outras tarefas a realizar. Além disso, se o programa tentar executar essas outras tarefas, poderá demorar muito para que o programa verifique novamente, resultando em perda de dados. Os engenheiros fizeram com que os periféricos interrompessem a CPU. As interrupções tiveram que ser priorizadas, porque a CPU só pode executar código para um periférico por vez, e alguns dispositivos são mais críticos em termos de tempo do que outros.

Os sistemas de ponta introduziram a ideia de controladores de canal, que eram essencialmente pequenos computadores dedicados a lidar com a entrada e saída de um determinado barramento. A IBM os introduziu no IBM 709 em 1958 e eles se tornaram um recurso comum em suas plataformas. Outros fornecedores de alto desempenho, como a Control Data Corporation, implementaram projetos semelhantes. Geralmente, os controladores de canal fariam o possível para executar todas as operações do barramento internamente, movendo os dados quando a CPU estivesse ocupada em outro lugar, se possível, e apenas usando interrupções quando necessário. Isso reduziu bastante a carga da CPU e proporcionou melhor desempenho geral do sistema.

Para fornecer modularidade, os barramentos de memória e E/S podem ser combinados em um barramento de sistema unificado.[7] Neste caso, um único sistema mecânico e elétrico pode ser usado para conectar muitos dos componentes do sistema ou, em alguns casos, todos eles.

Posteriormente, programas de computador começaram a compartilhar memória comum a várias CPUs. O acesso a esse barramento de memória também teve que ser priorizado. A maneira simples de priorizar interrupções ou acesso ao barramento era com uma ligação em série. Neste caso, os sinais fluirão naturalmente através do barramento em ordem física ou lógica, eliminando a necessidade de agendamento complexo.

Minis e micros

editarA Digital Equipment Corporation (DEC) reduziu ainda mais o custo dos minicomputadores produzidos em massa e mapeou periféricos no barramento de memória, de modo que os dispositivos de entrada e saída pareciam ser locais de memória. Isso foi implementado no Unibus do PDP-11 por volta de 1969.[8]

Os primeiros sistemas de barramento de microcomputadores eram essencialmente um backplane passivo conectado diretamente ou através de amplificadores de buffer aos pinos da CPU. Memória e outros dispositivos seriam adicionados ao barramento usando o mesmo endereço e pinos de dados usados pela própria CPU, conectados em paralelo. A comunicação era controlada pela CPU, que lia e escrevia os dados dos dispositivos como se fossem blocos de memória, utilizando as mesmas instruções, todas cronometradas por um relógio central que controlava a velocidade da CPU. Ainda assim, os dispositivos interromperam a CPU sinalizando em pinos separados da CPU.

Por exemplo, um controlador de unidade de disco sinalizaria à CPU que novos dados estavam prontos para serem lidos, momento em que a CPU moveria os dados lendo o "local de memória" que correspondia à unidade de disco. Quase todos os primeiros microcomputadores foram construídos desta forma, começando com o barramento S-100 no sistema de computador Altair 8800.

Em alguns casos, principalmente no IBM PC, embora uma arquitetura física semelhante possa ser empregada, as instruções para acessar periféricos (in e out) e memória (mov e outros) não foram uniformizadas e ainda geram sinais de CPU distintos, que poderiam ser usado para implementar um barramento de E/S separado.

Esses sistemas de barramento simples apresentavam uma séria desvantagem quando usados em computadores de uso geral. Todos os equipamentos do barramento tinham que falar na mesma velocidade, pois compartilhavam um único relógio.

Aumentar a velocidade da CPU fica mais difícil, pois a velocidade de todos os dispositivos também deve aumentar. Quando não é prático ou econômico ter todos os dispositivos tão rápidos quanto a CPU, a CPU deve entrar em um estado de espera ou trabalhar temporariamente em uma frequência de clock mais lenta,[9] para se comunicar com outros dispositivos no computador. Embora aceitável em sistemas embarcados, esse problema não foi tolerado por muito tempo em computadores de uso geral expansíveis pelo usuário.

Esses sistemas de barramento também são difíceis de configurar quando construídos a partir de equipamentos comuns disponíveis no mercado. Normalmente, cada placa de expansão adicionada requer muitos jumpers para definir endereços de memória, endereços de E/S, prioridades de interrupção e números de interrupção.

Segunda geração

editarSistemas de barramento de “segunda geração”, como o NuBus, resolveram alguns desses problemas. Eles normalmente separavam o computador em dois “mundos”, a CPU e a memória de um lado e os vários dispositivos do outro. Um controlador de barramento aceitava que dados do lado da CPU fossem movidos para o lado dos periféricos, transferindo assim a carga do protocolo de comunicação da própria CPU. Isso permitiu que o lado da CPU e da memória evoluísse separadamente do barramento do dispositivo, ou apenas "barramento". Os dispositivos no barramento poderiam se comunicar entre si sem intervenção da CPU. Isso levou a um desempenho muito melhor no "mundo real", mas também exigiu que os cartões fossem muito mais complexos. Esses barramentos também frequentemente abordavam problemas de velocidade por serem "maiores" em termos de tamanho do caminho de dados, passando de barramentos paralelos de 8 bits na primeira geração para 16 ou 32 bits na segunda, além de adicionar configuração de software (agora padronizado como Plug-n-play) para suplantar ou substituir os jumpers.

No entanto, estes sistemas mais recentes partilhavam uma qualidade com os seus primos anteriores: todos no autocarro tinham de falar à mesma velocidade. Embora a CPU agora estivesse isolada e pudesse aumentar a velocidade, as CPUs e a memória continuaram a aumentar em velocidade muito mais rápido do que os barramentos com os quais conversavam. O resultado foi que as velocidades do barramento eram agora muito mais lentas do que o necessário para um sistema moderno, e as máquinas ficaram carentes de dados. Um exemplo particularmente comum desse problema foi que as placas de vídeo rapidamente ultrapassaram até mesmo os sistemas de barramento mais recentes, como o PCI, e os computadores começaram a incluir AGP apenas para controlar a placa de vídeo. Em 2004, o AGP foi superado novamente por placas de vídeo de última geração e outros periféricos e foi substituído pelo novo barramento PCI Express.

Um número crescente de dispositivos externos também começou a empregar seus próprios sistemas de barramento. Quando as unidades de disco foram introduzidas pela primeira vez, elas eram adicionadas à máquina com uma placa conectada ao barramento, e é por isso que os computadores têm tantos slots no barramento. Mas durante as décadas de 1980 e 1990, novos sistemas como SCSI e IDE foram introduzidos para atender a essa necessidade, deixando vazias a maioria dos slots nos sistemas modernos. Hoje é provável que haja cerca de cinco barramentos diferentes em uma máquina típica, suportando vários dispositivos.[carece de fontes]

Terceira geração

editarOs barramentos de "terceira geração" têm surgido no mercado desde cerca de 2001, incluindo HyperTransport e InfiniBand. Eles também tendem a ser muito flexíveis em termos de conexões físicas, permitindo que sejam utilizados tanto como barramentos internos, quanto para conectar diferentes máquinas entre si. Isso pode levar a problemas complexos ao tentar atender a diferentes solicitações; portanto, grande parte do trabalho nesses sistemas diz respeito ao design de software, e não ao hardware em si. Em geral, esses barramentos de terceira geração tendem a se parecer mais com uma rede do que com o conceito original de barramento, com uma sobrecarga de protocolo mais alta necessária do que os sistemas anteriores, ao mesmo tempo que permitem que vários dispositivos usem o barramento ao mesmo tempo.

Barramentos como o Wishbone foram desenvolvidos pelo movimento de hardware de código aberto na tentativa de remover ainda mais as restrições legais e de patentes do design de computadores.

O Compute Express Link (CXL) é uma interconexão de padrão aberto para CPU para dispositivo e CPU para memória de alta velocidade, projetada para acelerar o desempenho do data center da próxima geração.[10]

Exemplos de barramentos internos de computador

editarParalelo

editar- Asus Media Bus proprietário, usado em algumas placas-mãe Asus Socket 7

- Computer Automated Measurement and Control (CAMAC) para sistemas de instrumentação

- Extended ISA ou EISA

- Industry Standard Architecture ou ISA

- Low Pin Count ou LPC

- MBus

- MicroChannel ou MCA

- Multibus para sistemas industriais

- NuBus ou IEEE 1196

- OPTi local bus usado nas primeiras placas-mãe Intel 80486.

- Peripheral Component Interconnect ou Conventional PCI

- Parallel ATA (também conhecido como Advanced Technology Attachment, ATA, PATA, IDE, EIDE, ATAPI, etc.), unidade de disco rígido, unidade de disco óptico, barramento de conexão periférica de unidade de fita

- S-100 bus ou IEEE 696, usado no Altair 8800 e microcomputadores similares

- SBus ou IEEE 1496

- SS-50 Bus

- Runway bus, um barramento de CPU frontal proprietário desenvolvido pela Hewlett-Packard para uso por sua família de microprocessadores PA-RISC

- GSC/HSC, um barramento periférico proprietário desenvolvido pela Hewlett-Packard para uso por sua família de microprocessadores PA-RISC

- Precision Bus, um barramento proprietário desenvolvido pela Hewlett-Packard para uso em sua família de computadores HP3000

- STEbus

- STD Bus (para STD-80 [8 bits] e STD32 [16/32 bits]), FAQ Arquivado em 2012-02-27 no Wayback Machine

- Unibus, um barramento proprietário desenvolvido pela Digital Equipment Corporation para seus computadores PDP-11 e VAX.

- Q-Bus, um barramento proprietário desenvolvido pela Digital Equipment Corporation para seus computadores PDP e posteriores VAX.

- VESA Local Bus ou VLB ou VL-bus

- VMEbus, o barramento VERSAmódulo Eurocard

- PC/104

- PC/104-Plus

- PCI-104

- PCI/104-Express

- PCI/104

- Zorro II e Zorro III, usados em sistemas computacionais Amiga

Serial

editarMuitos barramentos de campo são barramentos de dados seriais (não devem ser confundidos com a seção paralela de "barramento de dados" de um barramento de sistema ou placa de expansão), vários dos quais usam as características elétricas RS-485 e então especificam seu próprio protocolo e conector:

- CAN bus ("Controller Area Network")

- Modbus

- ARINC 429

- MIL-STD-1553

- IEEE 1355

Outros barramentos seriais incluem:

- Camera Link

- eSATA

- ExpressCard

- Inferface IEEE 1394 (FireWire)

- RS-232

- Thunderbolt

- USB

Exemplos de barramentos de computador internos/externos

editar- Small Computer System Interface (SCSI), unidade de disco rígido e barramento de conexão periférica de unidade de fita

- Serial Attached SCSI (SAS) e outros barramentos SCSI seriais

- Thunderbolt

- Yapbus, um barramento proprietário desenvolvido para o Pixar Image Computer

Ver também

editar

Referências

- ↑ Clifton, Carl (19 de setembro de 1986). What Every Engineer Should Know about Data Communications. [S.l.]: CRC Press. p. 27. ISBN 9780824775667. Cópia arquivada em 17 de janeiro de 2018.

The internal computer bus is a parallel transmission scheme; within the computer....

- ↑ Hollingdale, Stuart H. (19 de setembro de 1958). Session 14. Data Processing. Applications of Computers, University of Nottingham 15-19 September 1958

- ↑ «bus Definition from PC Magazine Encyclopedia». pcmag.com. 29 de maio de 2014. Consultado em 21 de dezembro de 2023. Cópia arquivada em 7 de fevereiro de 2015

- ↑ Avionic Systems Standardisation Committee, Guide to Digital Interface Standards For Military Avionic Applications, ASSC/110/6/2, Issue 2, September 2003

- ↑ a b Don Lancaster. "TV Typewriter Cookbook". (TV Typewriter). Section "Bus Organization". p. 82.

- ↑ McCann, Doug; Thorne, Peter (2000). The Last of The First, CSIRAC: Australias First Computer. [S.l.]: University of Melbourne Computing Science. pp. 8–11,13,91. ISBN 0-7340-2024-4

- ↑ Linda Null; Julia Lobur (2006). The essentials of computer organization and architecture 2nd ed. [S.l.]: Jones & Bartlett Learning. pp. 33,179–181. ISBN 978-0-7637-3769-6. Cópia arquivada em 17 de janeiro de 2018

- ↑ C. Gordon Bell; R. Cady; H. McFarland; B. Delagi; J. O'Laughlin; R. Noonan; W. Wulf (1970). A New Architecture for Mini-Computers—The DEC PDP-11 (PDF). Spring Joint Computer Conference. pp. 657–675. Cópia arquivada (PDF) em 27 de novembro de 2011

- ↑ Bray, Andrew C.; Dickens, Adrian C.; Holmes, Mark A. (1983). «28. The One Megahertz bus». The Advanced User Guide for the BBC Microcomputer. Cambridge, UK: Cambridge Microcomputer Centre. pp. 442–443. ISBN 0-946827-00-1. Consultado em 28 de março de 2008. Arquivado do original (zipped PDF) em 14 de janeiro de 2006

- ↑ «ABOUT CXL». Compute Express Link (em inglês). Consultado em 30 de dezembro de 2023